- 622.00 KB

- 2022-06-16 16:59:17 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

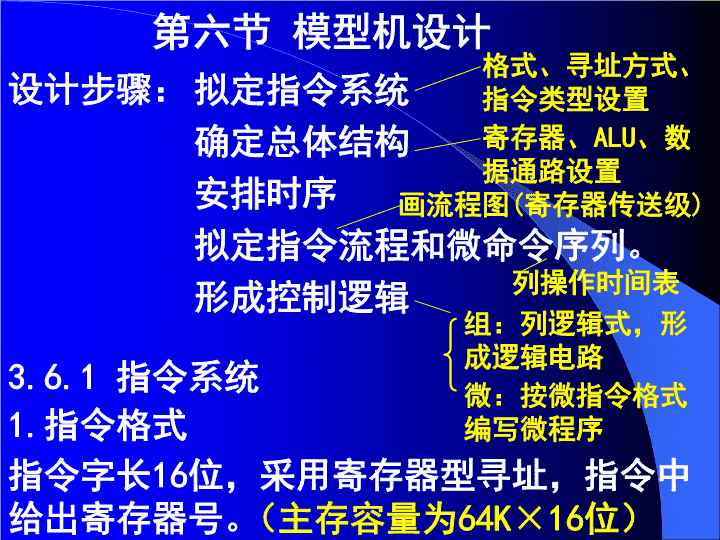

第六节模型机设计设计步骤:拟定指令系统确定总体结构安排时序拟定指令流程和微命令序列。形成控制逻辑3.6.1指令系统1.指令格式格式、寻址方式、指令类型设置寄存器、ALU、数据通路设置画流程图(寄存器传送级)列操作时间表组:列逻辑式,形成逻辑电路微:按微指令格式编写微程序指令字长16位,采用寄存器型寻址,指令中给出寄存器号。(主存容量为64K×16位)

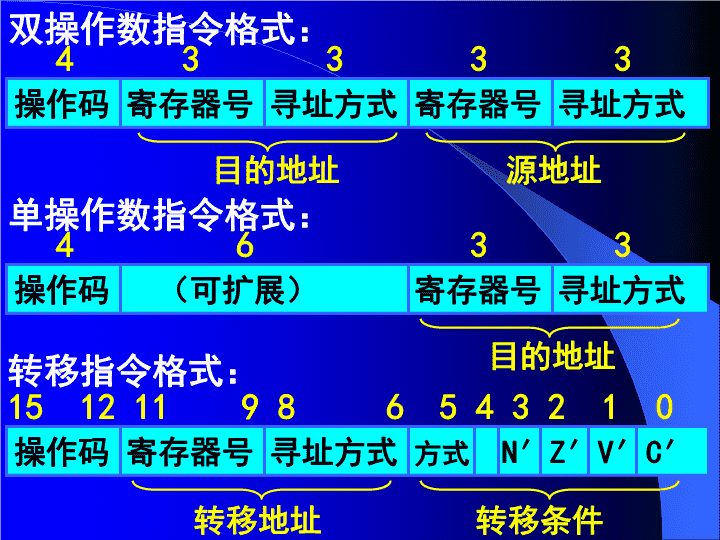

双操作数指令格式:4633操作码寄存器号寻址方式寄存器号寻址方式目的地址源地址单操作数指令格式:操作码(可扩展)寄存器号寻址方式43333目的地址转移指令格式:151211986543210转移地址转移条件操作码寄存器号寻址方式方式N′Z′V′C′

CPU可编程访问的寄存器:寻址方式编码助记符定义2.寻址方式寄存器寻址通用寄存器R、指令计数器PC、堆栈指针SP、程序状态字PSW000R(R)为操作数寄存器间址001(R)(R)为操作数地址自减型寄存器间址010-(R)-(SP)(R)-1为操作数地址(SP)-1为栈顶地址

寻址方式编码助记符定义101(PC)+(R)+d为有效地址(R)为操作数地址,立即/自增型寄存器间址011(R)+访问后(R)+1(SP)+(SP)为栈顶地址,出栈后(SP)+1(PC)为立即数地址,取数后(PC)+1变址X(R)X(PC)(PC)+d为有效地址跳步110SKP跳过下条指令执行

操作码助记符含义3.指令类型用于数传、堆栈、I/O操作0000MOV传送0001ADD加0101EOR异或双操作数指令0110COM求反1011SR右移单操作数指令1100JMP转移1100RST返回1101JSR转子

00000543210转移地址无条件转JMP寄寻方式N′Z′V′C′00001无进位转(C=0)00010无溢出转(V=0)00100数非零转(Z=0)01000数为正转(N=0)10001有进位转(C=1)10010有溢出转(V=1)10100数为零转(Z=1)11000数为负转(N=1)条件满足,转转移地址;条件不满足,顺序执行。

隐含约定:转子时返回地址压栈保存。15121198650子程序入口RSTSP(SP)+JSR寄寻方式N′Z′V′C′5432103.6.2CPU总体结构1.寄存器设置(1)可编程寄存器(16位)通用寄存器:R0(000)、R1(001)R2(010)、R3(011)

允许中断(开中断)(可扩展)INZVC43210暂存器C(2)非编程寄存器(16位)堆栈指针:SP(100)指令计数器:PC(111)程序状态字:PSW(101):暂存来自主存的源地址或源数据。暂存器D:暂存来自主存的目的地址或目的数。指令寄存器IR地址寄存器MAR数据寄存器MDR:存放现行指令。实现CPU与主存的接口

SN741814片SN741821片2.算逻部件设置ALU选择数据来源选择器A选择器B移位器:实现直送、左移、右移、字节交换3.数据通路结构为了使数据传送控制简单、集中,采用以ALU为中心的总线结构。(1)组成包括四个部分:ALU部件、寄存器组、内总线、CPU与系统总线的连接(16位)

R0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑(2)特点ALU为内部数据传送通路的中心;寄存器采用内总线采用单向数据总线(16位);分立结构;

与系统总线的连接通过MAR、MDR实现。MDR输入输出至DB输出至ALU的B门输出从内总线输入从DB输入(打入)(置入)R0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

4.各类信息传送途径M(1)指令信息置入DBIR(2)地址信息R0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

1)指令地址2)指令地址加1PC打入AALU移内MARPCAALU移内PCC0打入R0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

3)转移地址寄存器寻址:R0打入BALU移内PC寄存器间址:R0打入BALU移内MARABMDB置入MDRB移、内PCALUR0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

4)操作数地址寄存器间址:R0打入BALU移内MARR0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

变址:R0PCAALU移内MARABMDB移内CMMDRBALUALUCAB移内MARR0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

(3)数据信息1)RR:R0打入BALU移内R1DBMDBMDRB移、内R2ALU2)RM:R0打入BALU内MDR3)MR:MR0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

4)MM:M(源)R0MDRDB内I/OALU5)RI/O:打入DBMDR内CALU(计算目的地址)DBMCALU内MDR(目的)R0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

DBDBDMA方式:I/O6)I/OR打入I/OMDR内R0ALU7)I/OMMR0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

5.微命令设置(1)数据通路操作:ALU功能选择:ALU输入选择:输出移位选择:结果分配:R0A、R0B、S3S2S1S0、M、C0不移、左移、CPR0、CPC、CPMAR、R0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

(2)访M、I/O操作:读R地址使能EMAR写W置入MDRSMDR,1MAR向AB送地址000MDR与DB断开,MAR与AB断开R=1读W=1写置入IRSIRR0~R3R0~R3CDCDSPPCPSWMDRA移位器BALUR2R0R1MI/OCB内总线CR3DMARMDRIRPCSPPSWABDB控制逻辑

3.6.3组合逻辑控制器设计1.时序系统(1)工作周期取指周期FT用于指令正常执行设置6个触发器分别作为各周期状态标志源周期ST目的周期DT执行周期ET中断周期ITDMA周期DMAT用于I/O传送控制1工作周期开始0工作周期结束在整个指令周期中,任何时候必须、且只能有一个工作周期状态标志为“1”。

1)取指周期FT从M取出指令并译码;公操作修改PC。3)目的周期DT4)执行周期ET取指结束时,按操作码和寻址方式(R/非R寻址)转相应工作周期。按寻址方式(非R寻址)形成源地址,从M取出源操作数,暂存于C。2)源周期ST按寻址方式(非R寻址)形成目的地址,或从M取出目的操作数,暂存于D。按操作码完成相应操作(传送、运算、取转移地址送入PC、返回地址压栈保存);后续指令地址送入MAR。

5)中断周期IT关中断、保存断点和PSW、转服务程序入口。由硬件完成1)时钟周期时间:IT指CPU响应中断请求后,到执行中断服务程序前。6)DMA周期DMAT一次从M读出,并经数据通路传送的操作;或一次数据通路传送操作;或一次向M写入的操作DMAT指CPU响应DMA请求后,到传送完一次数据。DMA控制器接管总线权,控制直传。(2)时钟周期(节拍)T1微秒完成一步操作:模型机以访存时间作为一步操作时间。一个总线周期等于一个时钟周期,可根据需要扩展。由硬件完成

2)时钟周期数:每个工作周期第一拍T=0,每开始一个新节拍T计数,工作周期结束时T清0。一个工作周期中的时钟数可变。用计数器T控制节拍数每个时钟结束时设置一个脉冲。(3)工作脉冲P1µSTP打入寄存器进行时序转换(周期状态设置/清除时钟T计数/清除)将计数值译码,可产生节拍电位。

2.控制流程(工作周期转换)FT双单转SRSTDRDTETDMATDMA请求?中断请求?ITSRDRYNYN

3.指令流程图与操作时间表(1)取指周期FT拟定指令流程:初始化时置入FT,确定各工作周期中每拍完成的具体操作(寄存器传送级)。列操作时间表:列出每一步操作所需的微命令及产生条件。1)进入FT的方式FTSRDCQQ总清1程序正常运行时同步打入FT。1FTCPFT

2)流程图1STFT0:PC+1PCMIR3)操作时间表FT0:电位型微命令脉冲型微命令MIREMAR,R,SIRPC+1PCPCA,A+1,DMCPPC1DT1ET或或CPFT(P)CPST(P)CPDT(P)CPET(P)CPT(P)工作周期中,每拍结束时发CPT;工作周期结束时,5个时序打入命令都发。转换

(2)传送指令FT0:PC+1PCMIR,1)流程图例1:MOVR0,R1;源数ET0:R1R0PCMARET1:例2:MOV(R0),(R1);FT0:MIR,PC+1PCST0:R1MARST1:MMDRCDT0:R0MAR目的地址ET0:CMDRET1:MDRMET2:PCMAR例3:MOVX(R0),X(R1);FT0:MIRPC+1PC

形地取源操作数,暂存于C,需5步。PC+1PCST0:PCMARDT1:MMDRCDT0:CMDR源数ET0:C+R1MARET1:MDRMET2:PCMARPC+1PC例3:MOVX(R0),X(R1);FT0:MIRMMDRCST1:ST2:ST3:ST4:PCMARMMDRD形地PC+1PCDT2:DT3:D+R0MAR目的地址取目的地址,暂存于MAR,需4步。源数送存储器,需3步。

FT0:MIR2)操作时间表例:MOV(R1),(SP)+;SPMARMMDRCPC+1PCCPPCST0:SP+1SPEMARRSMDRMDRB输出BDMCPCSPAA+1DMCPSPEMARPCAA+1RSIRDM1STCPFT(P)CPET(P)CPT(P)DMCPMAR输出ASPAT+1CPT(P)T+1CPT(P)ST1:ST2:1DTCPFT(P)CPET(P)CPT(P)

ET1:MDRMPCMARET2:EMARWT+1CPT(P)DMCPMAR输出APCA1FTCPFT(P)CPET(P)CPT(P)DT0:R1MARDMCPMAR输出AR1AT+1CPT(P)1ETCPFT(P)CPET(P)ET0:CMDRCB输出BDMCPMDRCPT(P)

(3)双操作数指令取目的数,暂存于D。例:ADDX(R1),(PC)+;FT0:MIR,PC+1PC立即数ST0:PCMARST1:MMDRCST2:PC+1PCDT0:PCMARDT1:MMDRDDT2:PC+1PC形式地址DT3:D+R1MARDT4:MMDRD目的数ET0:C+DMDRET1:MDRMET2:PCMAR

(4)单操作数指令FT0:MIR,例:COM-(R0);DT0:R0-1R0、MARDT1:MMDRDET0:ET1:MDRMET2:PCMARPC+1PCDMDR(5)转移-返回指令无条件转移SKPR(R)(R)+按R指示从M取转移地址,修改R。(SP)+X(PC)执行再下条指令。从R取转移地址。按R指示从M取转移地址。从堆栈取返回地址,修改SP。以PC內容为基准转移。(RST)

FT0:MIR,例1:JMPR0;SP+1SP、MARMMDRPCET0:ET1:SPMARET2:R0PCPC+1PC无条件转子:R(R)(R)+(SP)+(PC)+入口在R中例2:RST(SP)+;FT0:MIR,PC+1PCET0:、MAR例3:JMPX(PC);FT0:MIR,PC+1PCET0:PCMARET1:MMDRC位移量ET2:PC+CPC、MAR(5)转子指令入口在M中入口在堆栈中

SP-1SPMDRMST1:PCMDR归纳微命令,综合化简条件,用组合逻辑电路实现。读令R=在ST形成子程序入口;在ET保存返回地址,并转子程序入口。ST0:、MAR例:JSR(R2);FT0:MIR,PC+1PCET0:R2MARET1:MMDRC子程序入口CPC、MAR返回地址压栈ET2:ET3:4.控制逻辑例:FT0+MOV(ST1+ST4+……)CPPC=FT0+……P+MOV(ST2+DT2)XP+……

3.6.4微程序控制器设计1.时序系统P微指令周期微指令打入µIR二级时序:控制数据通路操作结果打入目的地,读取后续微指令后续微地址打入µAR

2.微指令格式按数据通路各段操作划分字段,同类操作中互斥的微命令放同一字段。(1)格式数据通路操作辅助操作AIBISMC0SZOEMARRWSTSC33522311124顺序控制访存操作(2)各字段功能1)数据通路操作AI:A输入选择000无输入001RiA010CA011DA100PCAR0~R3、SP、PC

AIBISMC0SZOEMARRWSTSC33522311124BI:B输入选择000无输入001RiB010CB011DB100MDRBSM:ALU功能选择S3S2S1S0MC0:初始进位选择S:移位选择ZO:结果分配001CPRiR0~R3、PSWR0~R3、SP、PC、PSW2)访存操作EMAR、R、W3)辅助操作00无操作01开中断10关中断11SIR

AIBISMC0SZOEMARRWSTSC335223111244)顺序控制增量断定0000顺序执行9种指明微地址形成方式SC:0001无条件转移0010按操作码分支0111转微子程序1000返回微主程序增量断定增量3.微程序的编制(1)编写顺序

按指令执行顺序编写:取机器指令SC=0000功能转移执行按操作码编码顺序,逐级分类编写:MOV指令、双操作数指令、单操作数指令、转移指令(2)实现分支将同类断定依据所对应的微地址放在相应的微地址形成表中,用SC字段选取。(见教材P161~P163)顺序执行现行微地址+1SC=0001无条件转现行微指令给出转移微地址SC=0111转微子程序现行微指令给出微子程序入口SC=1000返回微主程序从寄存器取返回微地址

微地址形成表:SC=0010按操作码分支(4路)表内单元地址SC=0011(断定依据):MOV执行规定操作后转取指入口双单元内容(微地址)单JMP/JSR03H取源数、目的地0CH取源数、目的数24H取目的数按J、PC分支3FH按操作码DR分支(24路)进入执行DRMOV06HDRMOV0AH双单3DH

SC=0100SC=01101)取指微指令代真从60H开始按J、PC分支(4路)40H46H顺序/转移地址PCSC=0101按源寻址方式分支(7路)4DH5EH按目的寻址方式分支(3)微指令实例AIBISMC0SZOEMARRWSTSC33522311124MIR:微地址00000000000000000000110110000

AIBISMC0SZOEMARRWSTSC3352231112400微地址01100000100100100111000000000PC+1PC:按操作码分支:微地址020000000000000000000000000102)机器指令的微程序实现例:MOVR1,(R0);按流程写出微地址0102034C4E4F0460050A0B080900

本章小结1、建立CPU整机概念逻辑组成工作机制(1)逻辑组成寄存器、ALU设置,数据通路结构(旧5.4.2,新3.4.3)(2)工作机制寄存器传送级:微操作控制级:各类指令的流程微命令序列指令的执行过程(旧5.5.2,新3.5.2)拟定流程的关键:清楚了解数据通路结构熟练掌握基本寻址方式

基本寻址方式(模型机):寄存器寻址:R自减型寄存器间址:–(R)自增型寄存器间址:(R)+立即寻址:(PC)+相对寻址:X(PC)–(SP)(用于入栈操作)(SP)+(用于出栈操作)(旧5.4.1,新3.4.2)寄存器间址:(R)变址:X(R)

(1)微命令的产生方式2、有关的基本概念组合逻辑控制方式:基本思想、优缺点、应用场合微程序控制方式:基本思想、优缺点、应用场合(旧5.5.4,新3.1.3、3.5.3)(旧5.6.1、5.8.1,新3.1.3、3.6.4)

(3)主机与外设的信息传送控制方式中断方式:DMA方式:(旧5.2.2,新3.1.4)定义、流程、应用场合定义、流程、应用场合(2)时序控制方式定义、特点、应用场合同步控制方式:异步控制方式:定义、特点、应用场合(旧5.3.1,新3.1.2)主设备、从设备

第三章复习提纲3.CPU组成(重在数据通路结构)。4.指令流程(寄存器传送级),操作时间表(微命令序列)。5.微指令设计方法(分段原则、各段功能、编码方法)。6.基本概念:溢出及判断方法,数的补码表示及变补,对阶,规格化,同步控制与异步控制(含义、应用场合),组合逻辑控制与微程序控制(基本思想、优缺点、应用场合),I/O传送控制方式(定义、应用场合),控制字,状态字,程序状态字,主设备,从设备……等。1.四种运算方法(原码一位乘、补码一位乘、原码加减交替除法、补码加减交替除法)的算法、规则。2.浮点加减运算流程。

1、分别写出下述指令流程:(1)MOVR2,(SP)+;(2)ADDX(PC),R1;(3)JMP(R0);2、列出指令JMP(R0);的取指周期和执行周期的操作时间表。假定执行周期结束后将进入新的取指周期。第三章作业(二)